【自动驾驶汽车通讯协议】深入理解PCI Express(PCIe)技术

自动驾驶汽车中的PCIe通讯协议介绍

文章目录

0. 前言

按照国际惯例,首先声明:本文只是我自己学习的理解,虽然参考了他人的宝贵见解及成果,但是内容可能存在不准确的地方。如果发现文中错误,希望批评指正,共同进步。

PCI Express(简称PCIe)是一种高速的计算机扩展总线标准。PCIe 由 Intel 公司于 2001 年提出,它被设计用于取代旧的PCI,AGP和PCI-X标准,并在现代计算机中广泛使用。然而,随着自动驾驶汽车技术的发展,PCIe协议在汽车电子架构中的重要性日益凸显。

这是因为自动驾驶系统需要处理大量的数据,包括来自各种传感器(如雷达、激光雷达、摄像头)的信息,以及高精度地图和定位数据。为了实现这种复杂的数据处理,车辆内部需要配备高性能计算平台,如GPU、FPGA或ASIC等加速器。这些计算资源通常通过PCIe总线连接,以提供必要的带宽和低延迟。

本文将深入探讨PCIe技术,尤其是在自动驾驶汽车中的应用。

1. PCIe简介

1.1 PCIe外观

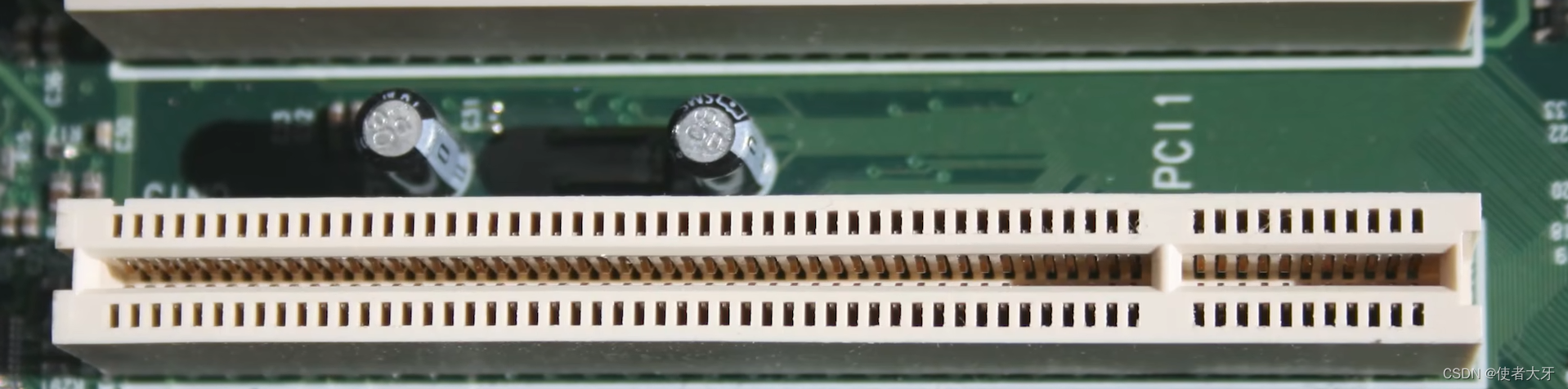

如果有拆过旧电脑的同学,可能会见到过这个接口:

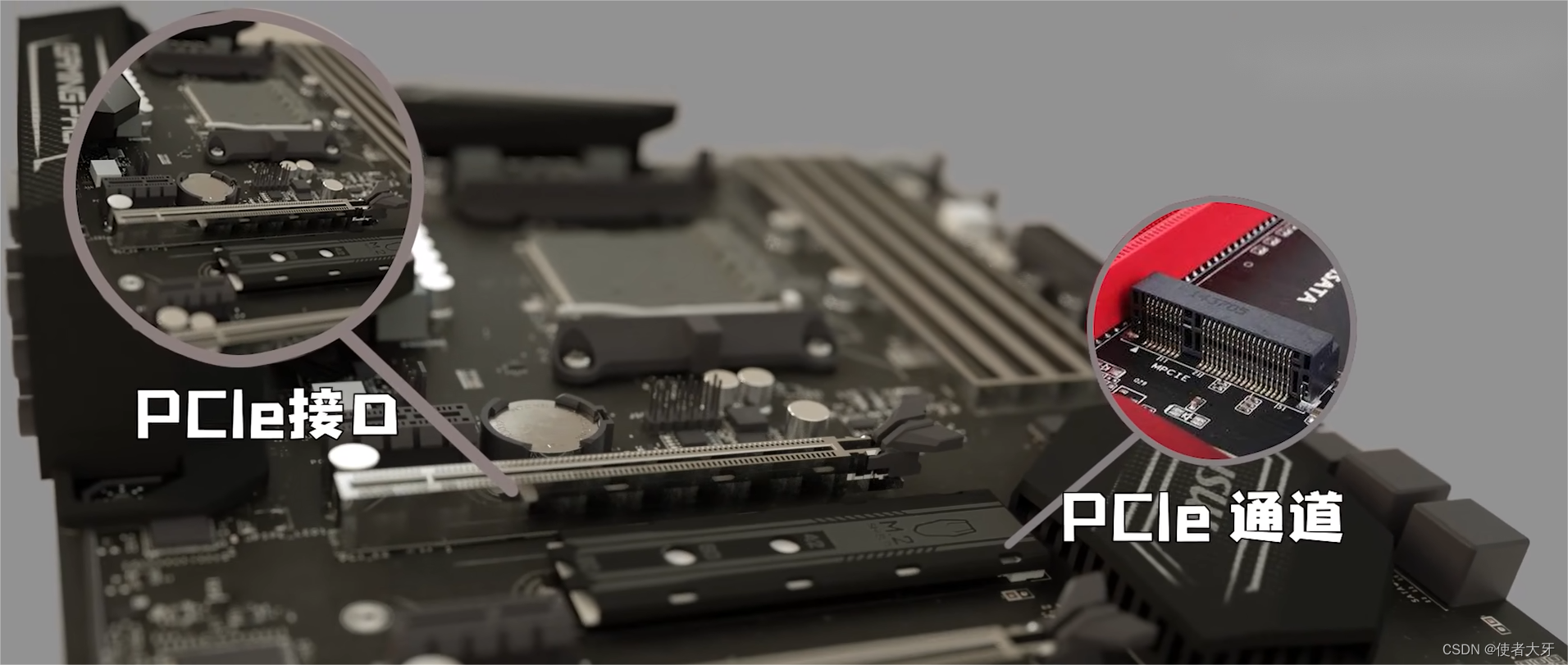

这便是PCI接口。而本文的主角PCIe是长下面的样子:

PCIe接口插槽的形状通常是矩形,边缘带有金属加固以增加耐用性。插槽的长度和宽度根据所支持的通道配置(如x1、x4、x8、x16等)而变化。较长的插槽支持更多的lane,因此具有更高的带宽。PCIe接口是主板上的插槽和相关的电气(如图形处理器(GPU)、网络适配器、固态硬盘(SSD)控制器、声卡等。)连接标准。

而PCIe通道是数据在设备与主板之间传输的具体路径。每个通道包含两对差分信号线(一对用于发送数据,另一对用于接收数据),允许全双工通信。

- 全双工通信(Full Duplex):通信的两端都可以同时发送和接收信息。这种模式通常使用两条独立的信道或者通过先进的信号处理技术在单一信道上实现,以避免信号之间的干扰。全双工通信在很多现代通信系统中都很常见,比如电话网络、以太网和无线局域网(Wi-Fi)。

- 半双工通信(Half Duplex):半双工通信允许双向通信,但是不能同时进行。在任一时刻,一个端点要么发送要么接收,而另一个端点则相反。典型的例子是步话机或对讲机,用户需要按下按钮才能发送信息,在发送时无法接收对方的回应。

1.2 PCIe的技术迭代

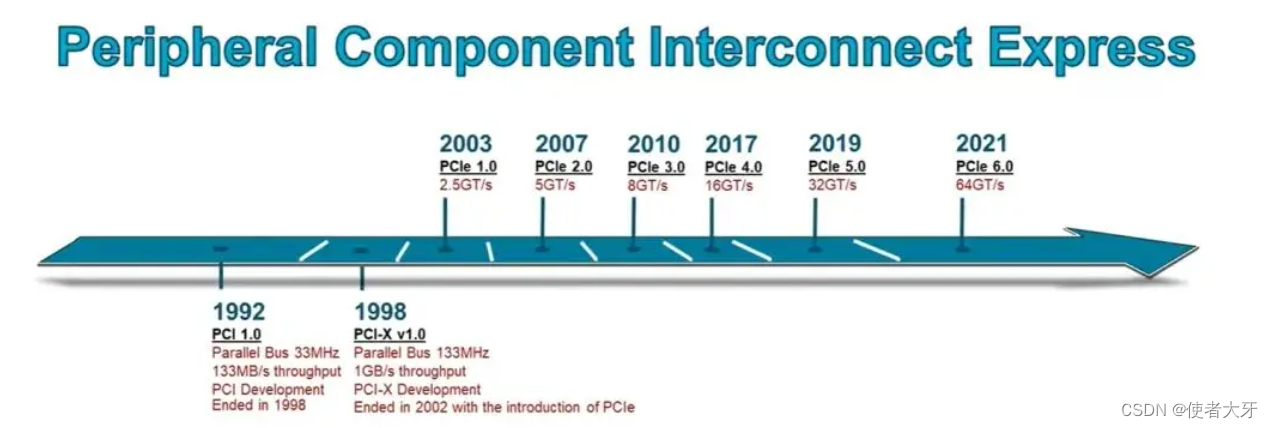

根据PCI-SIG(PCI特别兴趣小组)制定的PCIe标准:PCIe现在已经出到了6.0版本。

2. PCIe的通道(lane)配置

PCI Express(PCIe)的通道(lane)配置是决定PCIe设备性能的关键因素。通道配置通常用“x”后跟一个数字表示,如x1、x4、x8、x16等,这个数字代表了有多少个独立的PCIe通道被使用,即有几个lane。这些配置影响了设备的带宽和数据传输速率,从而影响了整体的系统性能。

2.1 通道配置详解

-

x1:这是最小的通道配置,只使用一个PCIe通道。尽管带宽最低,但它足够用于低带宽需求的设备,如一些网络适配器、声卡或USB扩展卡。

-

x4:使用四个PCIe通道,提供了四倍于x1配置的带宽。这样的配置常用于需要更高带宽但又不需要x8或x16带宽的设备,如某些高速的存储解决方案或中等带宽需求的网络卡。

-

x8:配置有八个PCIe通道,提供了八倍于x1配置的带宽。x8通常用于高性能的存储设备,如RAID控制器。

-

x16:这是最常见的高性能配置,使用16个PCIe通道,提供了16倍于x1配置的带宽。x16配置主要用于图形卡(GPU),因为这些设备需要非常高的带宽来处理大量的图形数据。

-

x32:虽然PCIe规范中定义了x32配置,但实际上很少见。理论上,x32配置将提供32倍于x1配置的带宽,但由于成本、功耗和设计复杂性,大多数系统中并未采用这种配置。

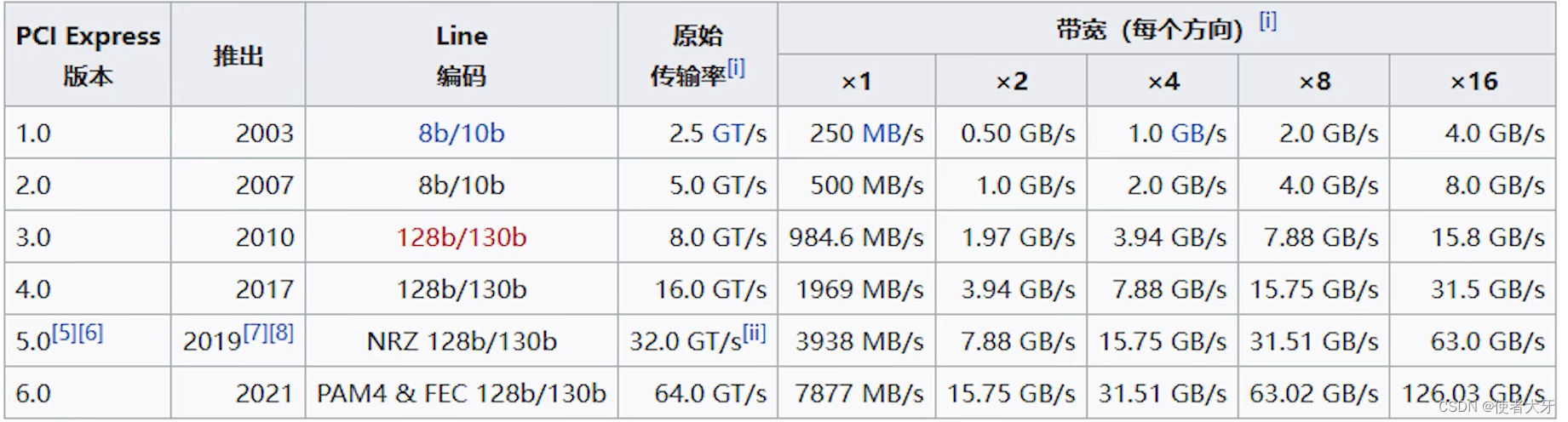

从下表可以直观看出通道数对带宽的影响,另外在不同的PCIe版本中单个通道的带宽也是不同的:

2.2 通道配置的影响

不同的通道配置对PCIe设备的性能有直接的影响。更高的通道数意味着更高的潜在带宽,这对于需要大量数据吞吐量的设备(如高端图形卡)至关重要。然而,更多的通道也会增加制造成本和功耗,因此对于不需要高带宽的设备,较低的通道配置通常是更经济的选择。

此外,通道配置还可以通过一种称为“通道拆分”或“bifurcation”的技术进行动态调整。这意味着一个物理上的x16插槽可以被配置为两个x8或一个x8和三个x4的组合,以适应不同的设备需求,同时优化系统资源的使用。这种灵活性使得PCIe架构能够更好地适应多样化的硬件需求。

3. PCIe的架构

3.1 架构层次

PCIe架构可以分为以下几层:

-

应用层:这不是PCIe规范正式定义的一部分,而是由具体实现者根据需求设计的部分,它决定了设备的功能和类型,例如存储设备、网络适配器或图形卡。

-

事务层(Transaction Layer):负责处理事务的初始化和完成,例如读取、写入、配置和中断等。事务层还管理事务的优先级和流量控制。

-

数据链路层(Data Link Layer):分为两个子层:链路子层(Link Sublayer)和物理媒体附件子层(Physical Media Attachment Sublayer)。链路子层负责链路的建立、训练、维护和错误检测,而物理媒体附件子层则负责数据的编码和解码。

-

物理层(Physical Layer):包括电气信号的生成、接收和处理,以及串行数据的编码和解码。物理层进一步细分为电气子层(Electrical Sublayer)和介质访问控制子层(Media Access Control Sublayer)。

3.2 核心组件

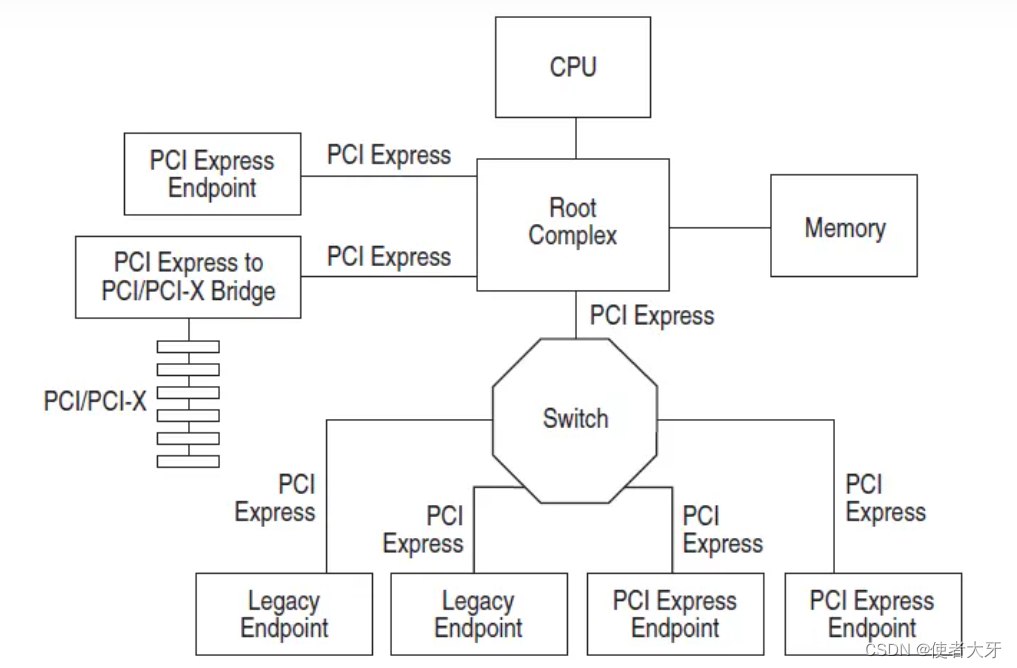

PCIe架构的核心组件包括:

-

Root Complex:通常位于系统主板上,与CPU紧密集成,作为PCIe架构的起点。Root Complex负责初始化和配置PCIe总线,管理事务,以及提供到CPU和内存的接口。

-

Switches:允许构建复杂的PCIe拓扑,通过连接多个端点设备或其它Switches,实现灵活的系统架构。Switches可以扩展PCIe总线,允许更多设备连接到系统中。

-

Endpoints:终端设备,如显卡、硬盘控制器或网络适配器,它们是PCIe总线的消费者,与Root Complex或Switches相连。

4. PCIe的特性

-

点对点连接:PCIe采用点对点连接,不同于共享总线架构,这减少了信号干扰,提高了带宽利用率。

-

动态链接速度和宽度:PCIe链接可以动态调整速度和宽度,以适应设备能力和系统需求。

-

热插拔:支持设备在系统运行时插入或移除,增强了系统的灵活性和可用性。

-

电源管理:包括设备的自动关闭和唤醒能力,有助于节省能源。

5. PCIe在自动驾驶中的应用

PCI Express (PCIe) 在自动驾驶汽车中扮演着关键角色,尤其是在那些依赖高性能计算和大量数据传输的场景中。自动驾驶汽车需要处理大量的传感器数据,包括摄像头、雷达、激光雷达(LiDAR)、超声波传感器等,这些数据需要被实时分析和处理,以做出准确的决策。PCIe 提供了必要的高速数据传输能力,使得这些数据能够在各个组件之间高效地流动。

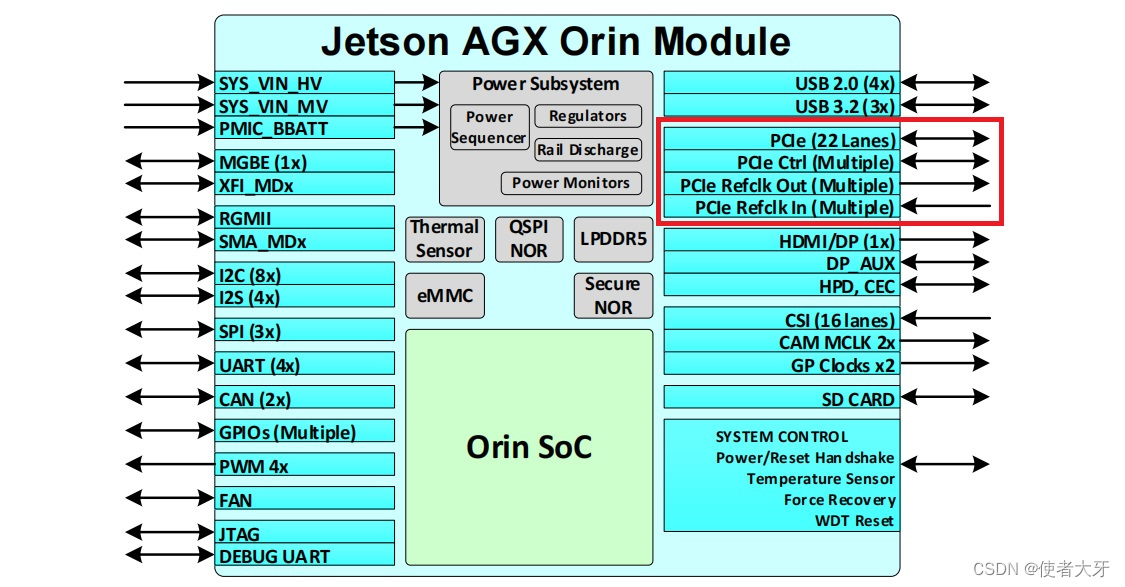

下图表示了NVIDIA Orin产品的接口,可以看出PCIe占了很重要的一部分:

例如,一辆配备了 8 个高清摄像头的自动驾驶汽车,每个摄像头输出的数据速率高达每秒数百兆字节。如果没有足够快的 PCIe 连接,数据处理可能会出现瓶颈,导致系统反应迟缓。因此,PCIe 在这个场景中是不可或缺的,它确保了数据的高速传输,使自动驾驶系统能够实时做出准确的决策。

以下是一些PCIe在自动驾驶汽车中具体的应用方向:

-

传感器数据聚合:

自动驾驶车辆装备了大量的传感器,每个传感器产生的数据流都必须被迅速地传输到中央处理器或数据处理单元。PCIe 提供了高带宽和低延迟的连接,使得传感器数据可以被快速地集中并处理。 -

高性能计算传输:

自动驾驶系统依赖于深度学习和人工智能算法,这些算法需要在GPU或专门的加速器上运行。PCIe 3.0 或更高级别的 PCIe 4.0 和 PCIe 5.0 可以提供足够的带宽来支持这些高负载的计算任务,确保数据在 CPU 和 GPU 或 FPGA 之间的高速传输。 -

域控制器和ECU的连接:

现代自动驾驶车辆可能包含多个域控制器(Domain Control Units),每个控制器负责不同的功能区域,如感知、规划和执行。这些控制器之间需要通过高速接口进行通信,PCIe 是一个理想的选项,因为它提供了可扩展性和灵活性。 -

冗余和安全性:

自动驾驶系统需要高度的可靠性和安全性。通过使用双路或冗余的 PCIe 连接,系统可以设计成即使某个链路失败也能保持运行,这对于保证车辆安全至关重要。 -

车载网络:

车载网络架构正从传统的基于CAN和FlexRay的架构向基于以太网和 PCIe 的更高带宽架构演进。PCIe 在这种架构中可以作为高速数据交换的核心,支持车辆内部的高速数据传输。

更多推荐

已为社区贡献3条内容

已为社区贡献3条内容

所有评论(0)