SJA1000 CAN总线控制器Verilog代码及三段式状态机实现(含中文注释与文档说明)

SJA1000 CAN总线控制器是汽车电子中常用的通信控制器,能够实现CAN总线协议的发送和接收功能。总之,这篇文章通过详细的代码和分析,为新手提供了一个完整的SJA1000 CAN总线控制器的实现方案,同时也为进一步的学习和实践提供了坚实的基础。在发送状态下,控制器会将数据通过CAN总线发送出去,一旦发送完成,控制器会进入应答状态,并通过can。接下来,让我们看看接收模块的设计。在顶层模块中,我

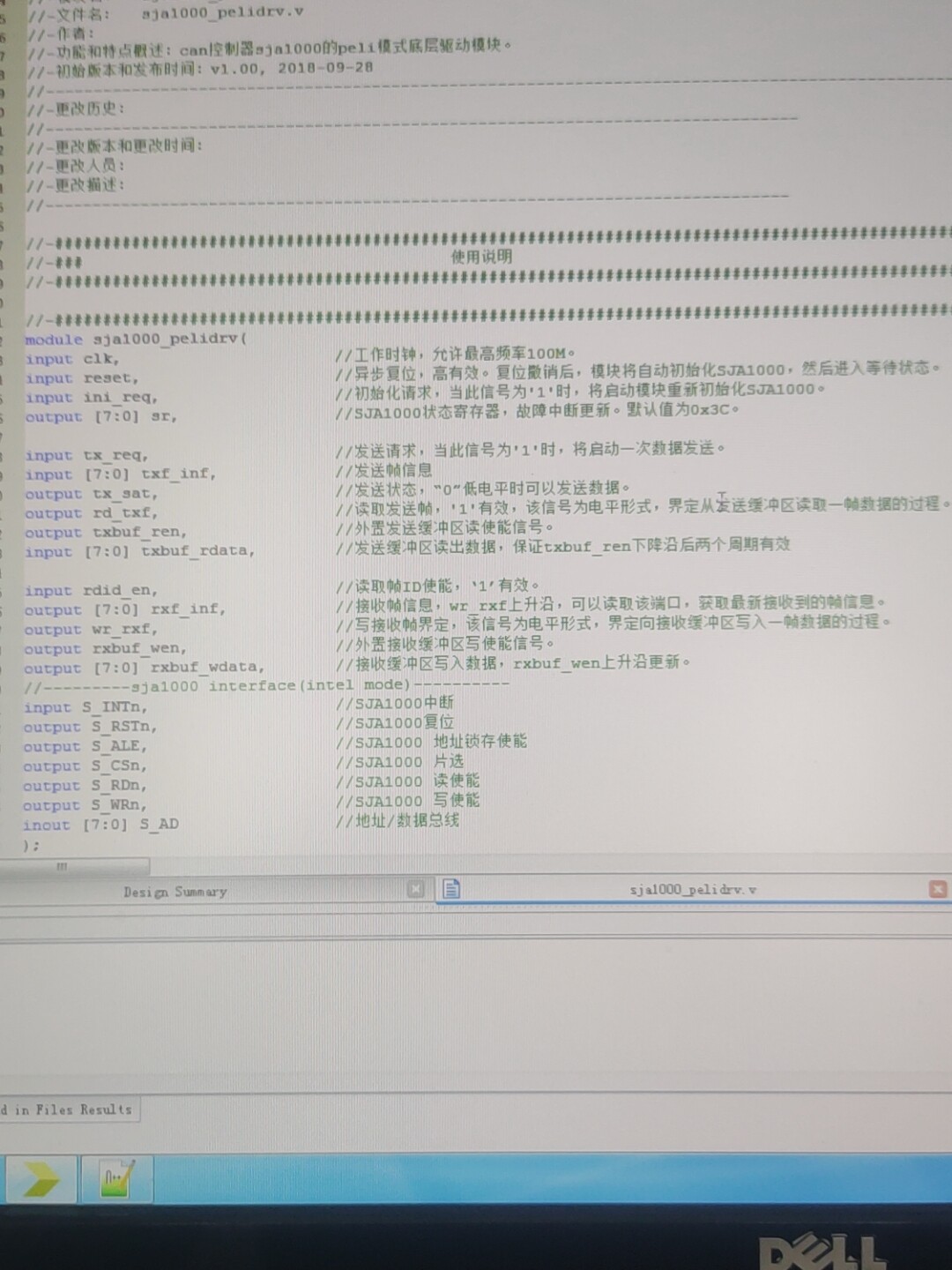

SJA1000 CAN总线verilog写的SJA1000 CAN总线控制器。 程序使用三段式状态机,对于语句均有箱子的中文注释,同时还有相关的文档说明。 可直接拿来使用,同时适合新手学习规范写作代码。

SJA1000 CAN总线控制器是汽车电子中常用的通信控制器,能够实现CAN总线协议的发送和接收功能。为了更好地理解和实现这个控制器,使用Verilog HDL进行设计是一个非常好的选择。今天,我将带大家一起探索如何用Verilog语言实现一个功能完善的SJA1000 CAN总线控制器,并通过代码和分析,帮助新手们更好地理解和学习。

首先,我们需要了解CAN总线的基本工作原理。CAN(Controller Area Network)是一种用于汽车和工业自动化的串行通信协议,具有高可靠性、实时性强和抗干扰能力强等特点。SJA1000是 Philips(现为NXP)公司生产的一款CAN控制器,广泛应用于汽车电子系统中。

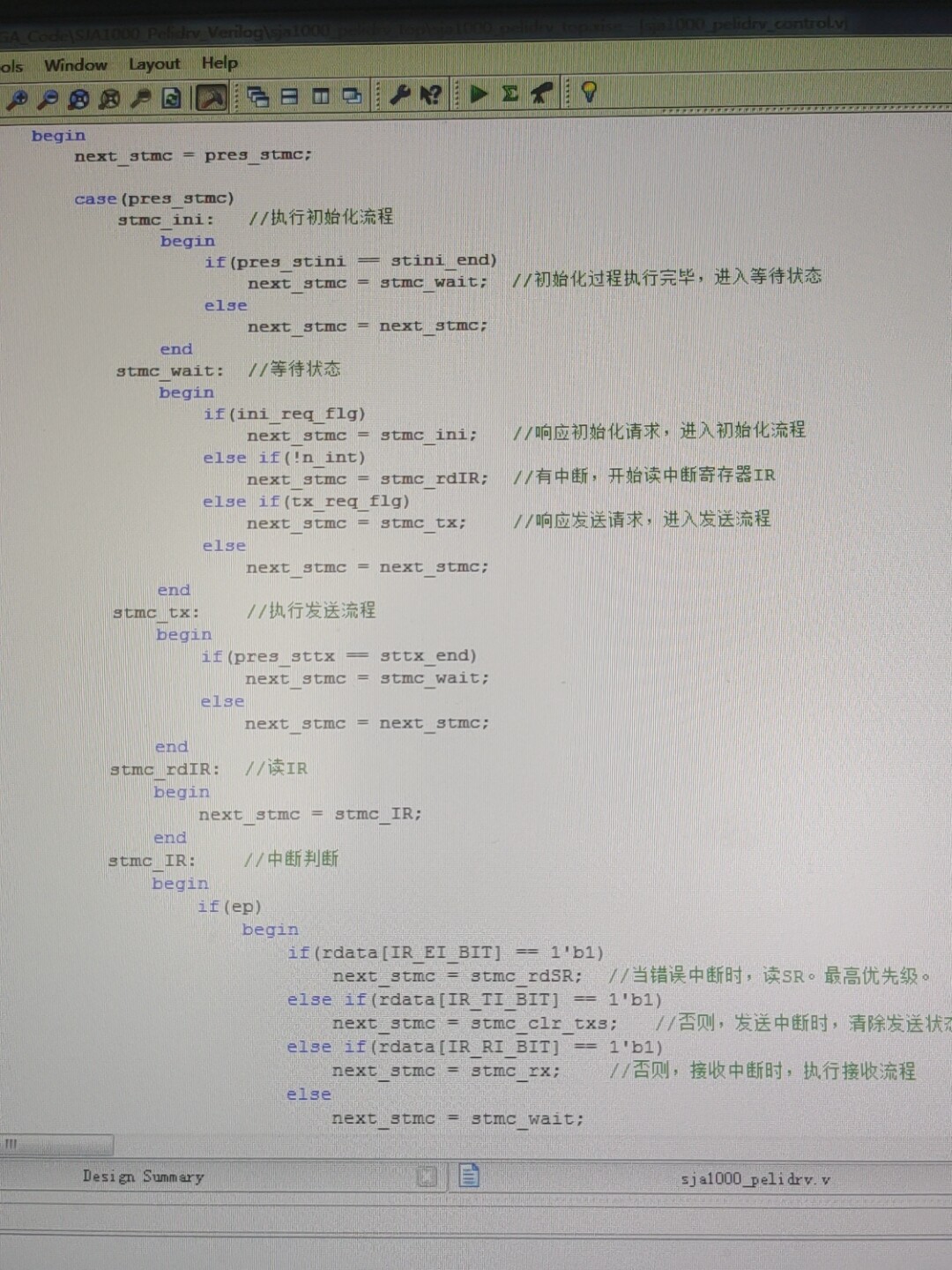

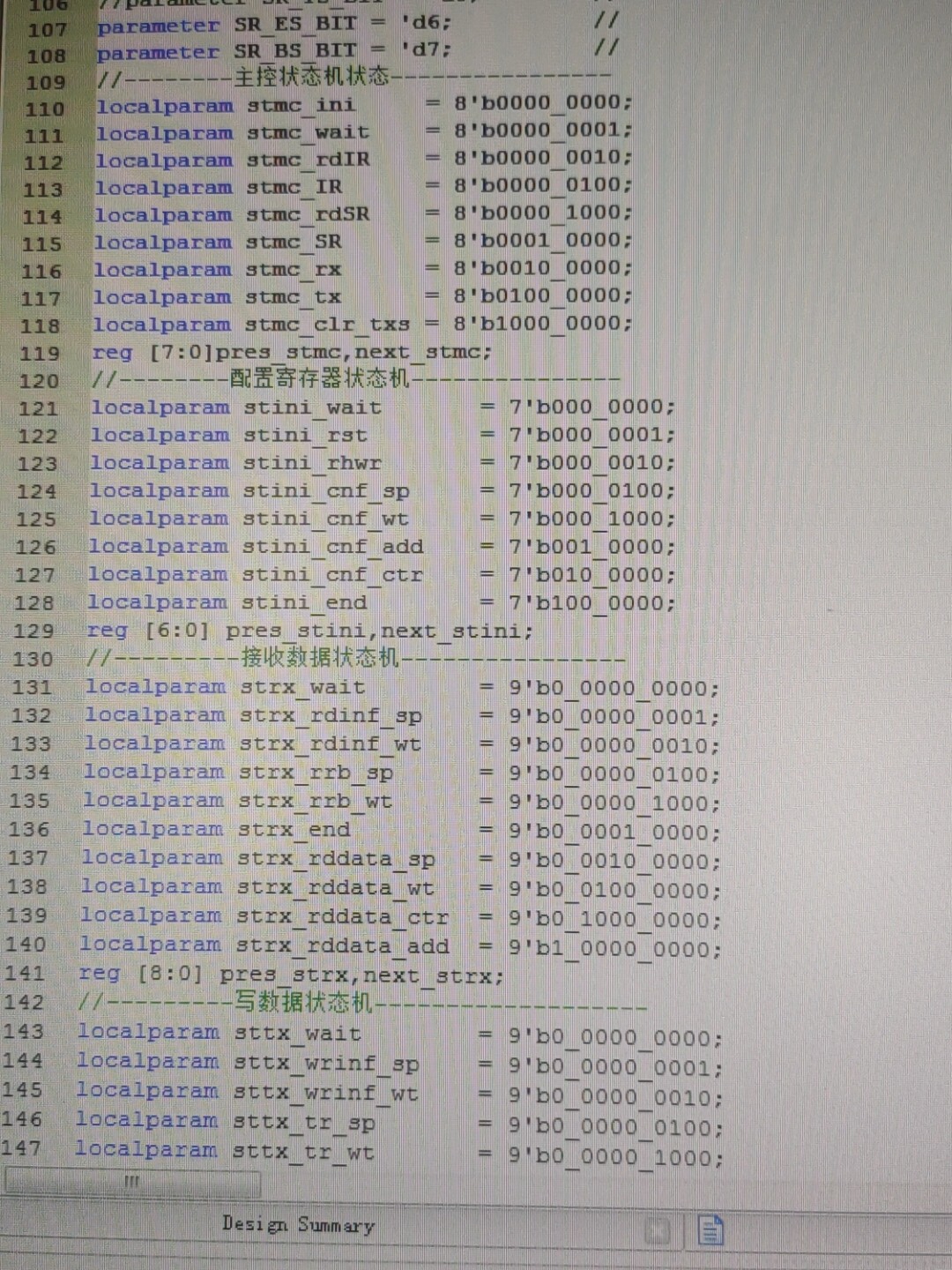

在Verilog实现SJA1000控制器时,我们可以采用三段式状态机设计。三段式状态机包括待机状态、发送状态和接收状态。这种设计方式清晰明了,适合新手学习和理解。

以下是发送模块的Verilog代码示例:

module can_send(

input wire clk, // 系统时钟

input wire rst_n, // 复位信号

input wire can_tx, // CAN发送使能信号

input wire [7:0] can_data, // CAN数据

output wire can_send_done // 发送完成信号

);

reg [7:0] send_data; // 发送数据寄存器

reg [2:0] state; // 状态寄存器

// 状态定义

localparam IDLE = 3'b000; // 待机状态

localparam SEND = 3'b001; // 发送状态

localparam ACK = 3'b010; // 应答状态

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

state <= IDLE;

send_data <= 8'b0;

end else begin

case(state)

IDLE: begin

if (can_tx) begin

state <= SEND;

send_data <= can_data;

end

end

SEND: begin

// 发送数据

if (can_send_done) begin

state <= ACK;

end

end

ACK: begin

state <= IDLE;

end

endcase

end

end

endmodule从代码中可以看到,我们使用了三个状态:待机(IDLE)、发送(SEND)和应答(ACK)。在待机状态下,当检测到CAN发送使能信号(cantx)时,控制器进入发送状态,并将要发送的数据加载到发送数据寄存器中。在发送状态下,控制器会将数据通过CAN总线发送出去,一旦发送完成,控制器会进入应答状态,并通过cansend_done信号通知上层模块发送完成。在应答状态下,控制器会自动回到待机状态,等待下一次发送请求。

接下来,让我们看看接收模块的设计。接收模块的实现与发送模块类似,但其主要功能是从CAN总线上接收数据并进行解析。以下是接收模块的Verilog代码示例:

module can_receive(

input wire clk, // 系统时钟

input wire rst_n, // 复位信号

input wire can_rx, // CAN接收使能信号

output wire [7:0] can_data // CAN接收数据

);

reg [7:0] recv_data; // 接收数据寄存器

reg [2:0] state; // 状态寄存器

// 状态定义

localparam IDLE = 3'b000; // 待机状态

localparam RECEIVE = 3'b001; // 接收状态

localparam STORE = 3'b010; // 存储状态

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

state <= IDLE;

recv_data <= 8'b0;

end else begin

case(state)

IDLE: begin

if (can_rx) begin

state <= RECEIVE;

end

end

RECEIVE: begin

// 接收数据

if (can_rx_done) begin

state <= STORE;

end

end

STORE: begin

can_data <= recv_data;

state <= IDLE;

end

endcase

end

end

endmodule在接收模块中,我们同样使用了三个状态:待机(IDLE)、接收(RECEIVE)和存储(STORE)。在待机状态下,当检测到CAN接收使能信号(canrx)时,控制器进入接收状态,并开始从CAN总线上读取数据。在接收完成后,控制器会进入存储状态,将接收到的数据存储到输出端口candata中,并自动回到待机状态,等待下一次接收请求。

除了发送和接收模块,我们还需要一个顶层模块来协调这两个模块的工作。顶层模块的主要功能是初始化CAN控制器、处理中断以及管理发送和接收模块的状态。以下是顶层模块的代码示例:

module can_controller(

input wire clk, // 系统时钟

input wire rst_n, // 复位信号

input wire can_tx, // CAN发送使能信号

input wire [7:0] can_data_in, // 输入数据

output wire can_send_done, // 发送完成信号

output wire [7:0] can_data_out // 输出数据

);

// 实例化发送模块

can_send u_send(

.clk(clk),

.rst_n(rst_n),

.can_tx(can_tx),

.can_data(can_data_in),

.can_send_done(can_send_done)

);

// 实例化接收模块

can_receive u_receive(

.clk(clk),

.rst_n(rst_n),

.can_rx(can_rx),

.can_data(can_data_out)

);

endmodule在顶层模块中,我们通过实例化发送模块和接收模块,并将其端口连接到顶层模块的输入输出端口,从而实现了CAN控制器的完整功能。

通过以上代码和分析,可以看出,使用Verilog实现SJA1000 CAN总线控制器的过程是清晰而系统的。三段式状态机的设计使得代码逻辑简单易懂,适合新手学习和理解。同时,代码中添加的详细中文注释和相关文档说明,使得代码的可读性和可维护性得到了极大的提升。

对于新手来说,学习和使用这个代码可以从以下几个方面入手:

- 理解CAN总线协议:首先需要了解CAN总线的基本原理和工作模式,包括数据帧的格式、仲裁机制、错误处理等。

- 学习Verilog语言:虽然这篇文章已经对代码进行了详细的解释,但为了更好地理解和修改代码,仍然需要掌握Verilog的基本语法和模块化设计方法。

- 仿真和调试:在实际使用中,可以通过Verilog仿真工具(如ModelSim、Vivado等)对代码进行仿真,观察各个信号的变化情况,确保代码的正确性。

- 实际应用:最后,可以将代码移植到FPGA或ASIC中,进行实际的硬件测试,验证控制器的功能和性能。

总之,这篇文章通过详细的代码和分析,为新手提供了一个完整的SJA1000 CAN总线控制器的实现方案,同时也为进一步的学习和实践提供了坚实的基础。希望大家能够通过这个例子,更加深入地理解CAN总线控制器的工作原理,并能够在实际项目中灵活运用所学知识。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)